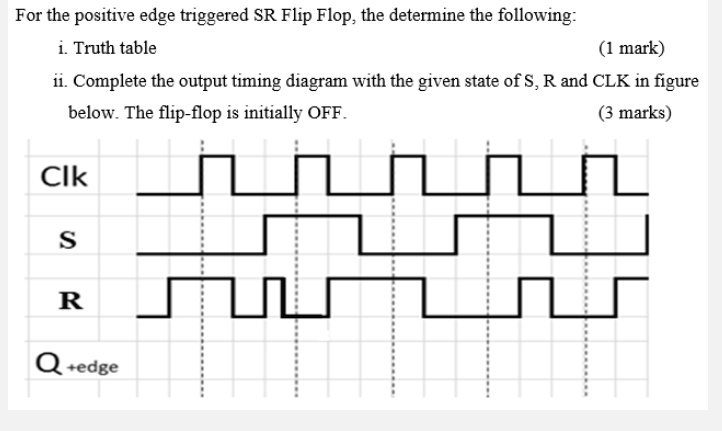

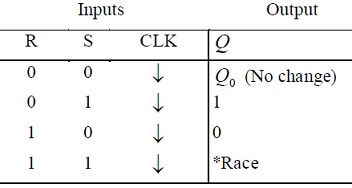

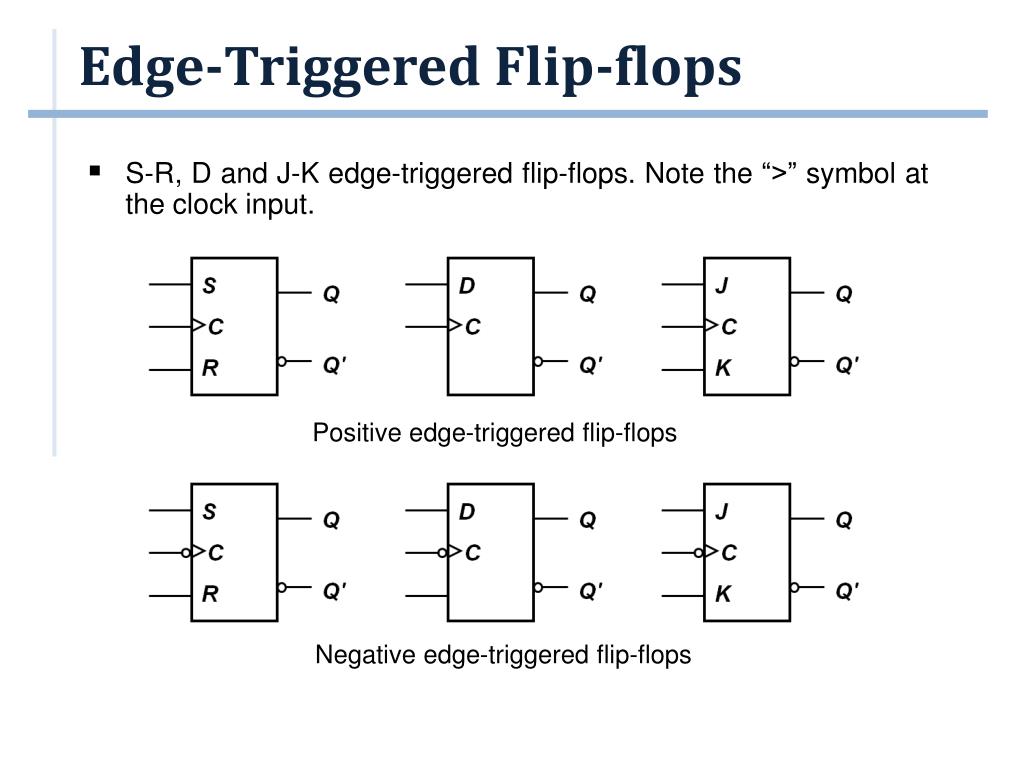

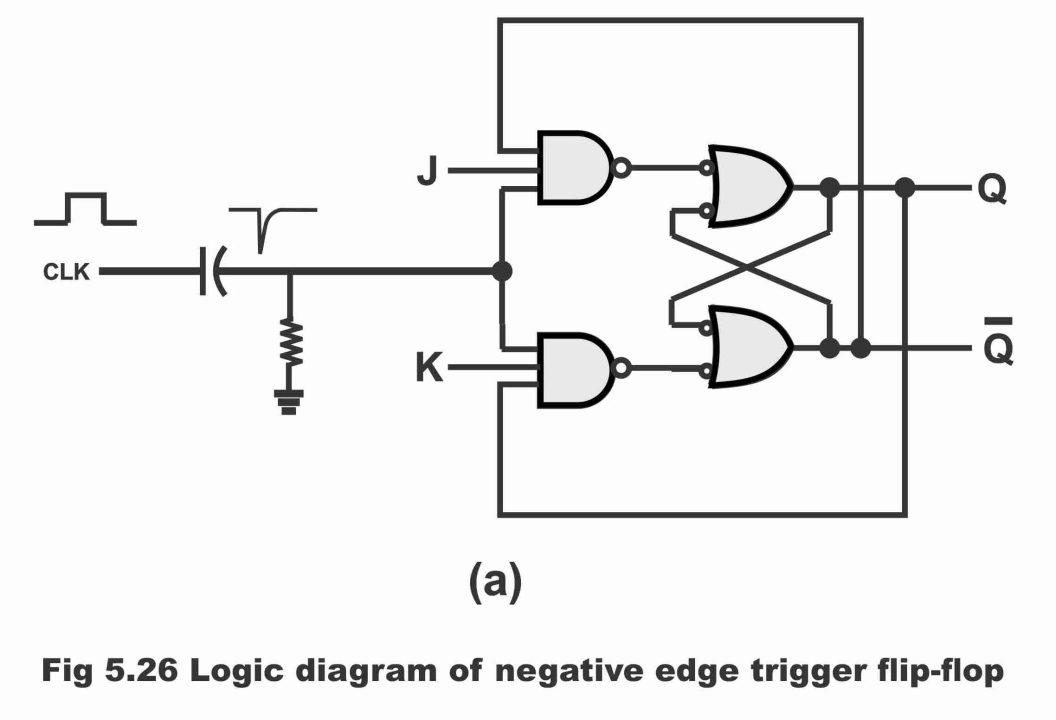

SOLVED: Clock and S, R waveforms are shown below for a negative edge-triggered SR flip flop. Sketch the output Q obtained in response to the input waveforms. Assume that the propagation delay

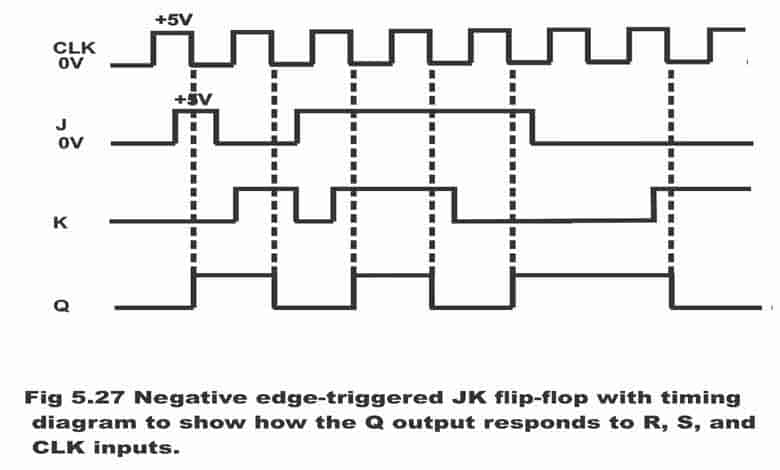

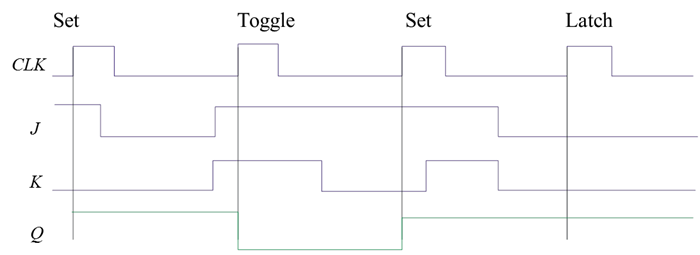

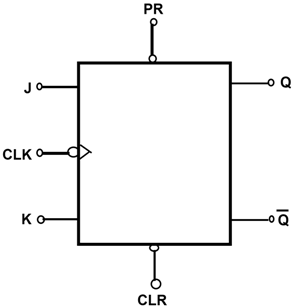

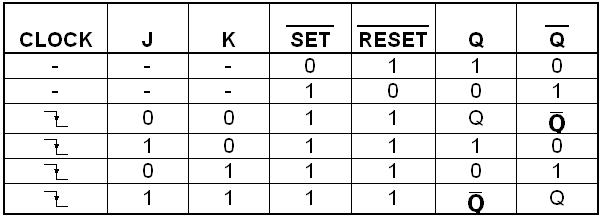

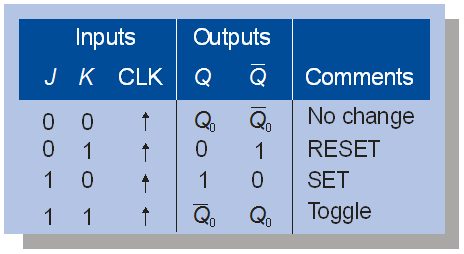

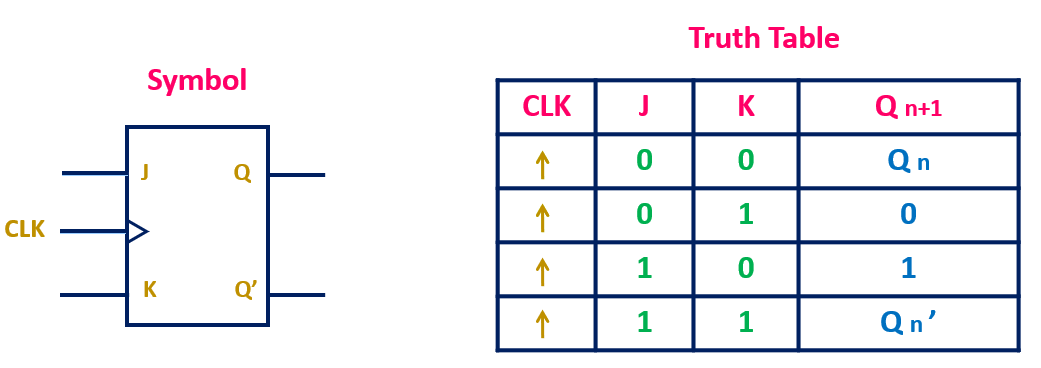

JK Flip-Flop Explained | Race Around Condition in JK Flip-Flop | JK Flip- Flop Truth Table, Excitation table and Timing Diagram - ALL ABOUT ELECTRONICS