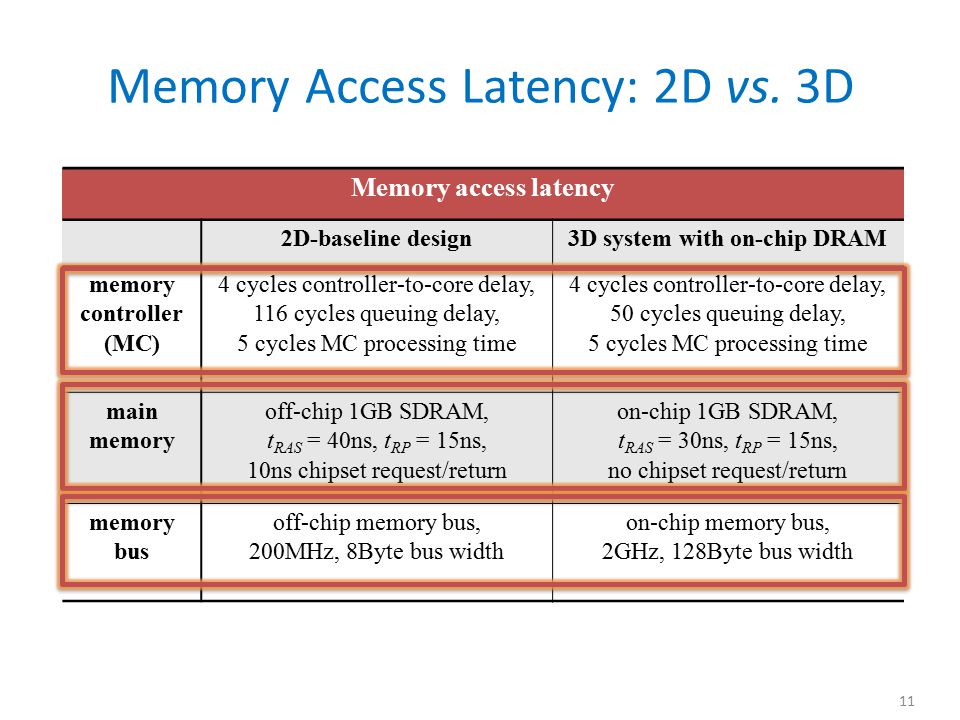

Illusion of large on-chip memory by networked computing chips for neural network inference | Nature Electronics

Electronics | Free Full-Text | Polymorphic Memory: A Hybrid Approach for Utilizing On-Chip Memory in Manycore Systems

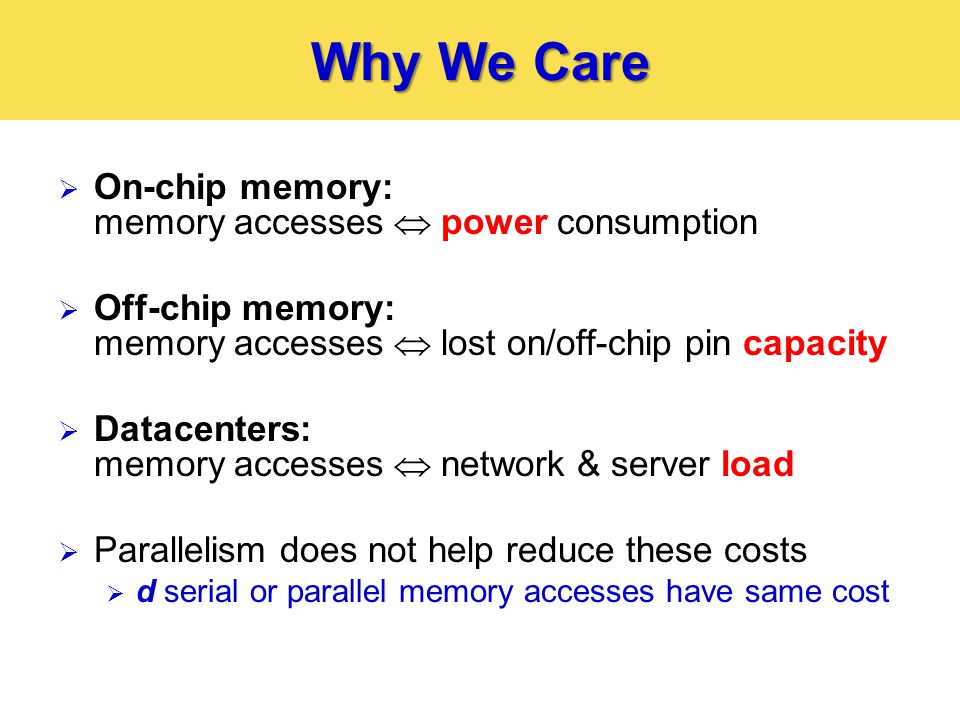

Optimal Fast Hashing Yossi Kanizo (Technion, Israel) Joint work with Isaac Keslassy (Technion, Israel) and David Hay (Hebrew Univ., Israel) - ppt download

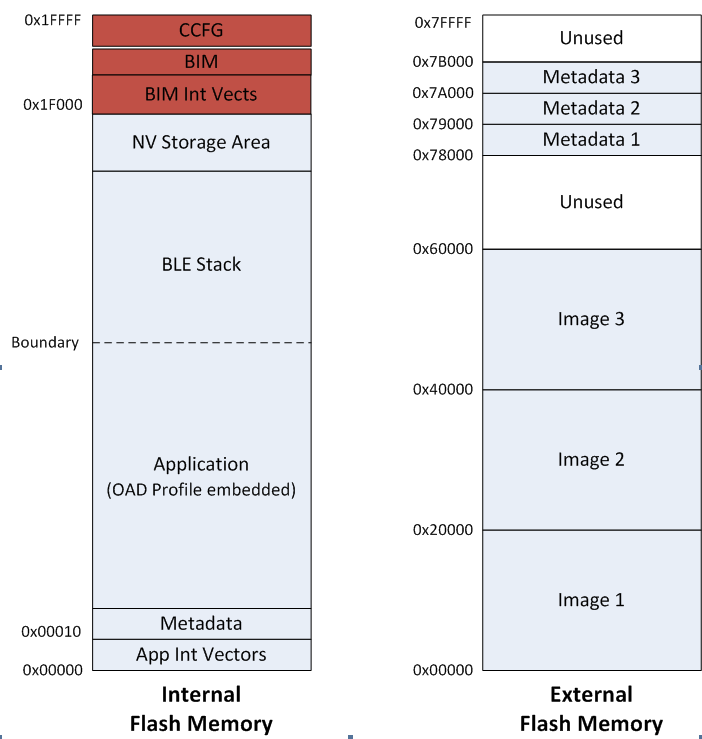

Figure 1 from On-chip vs. off-chip memory: the data partitioning problem in embedded processor-based systems | Semantic Scholar

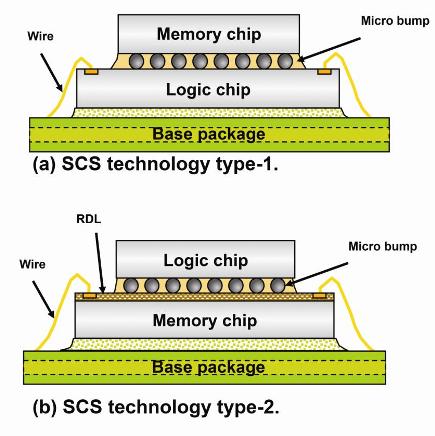

Figure 2 from On-chip vs. off-chip memory: the data partitioning problem in embedded processor-based systems | Semantic Scholar

![2102.11531] Memory-efficient Speech Recognition on Smart Devices 2102.11531] Memory-efficient Speech Recognition on Smart Devices](https://ar5iv.labs.arxiv.org/html/2102.11531/assets/figures/hwAbstract.png)