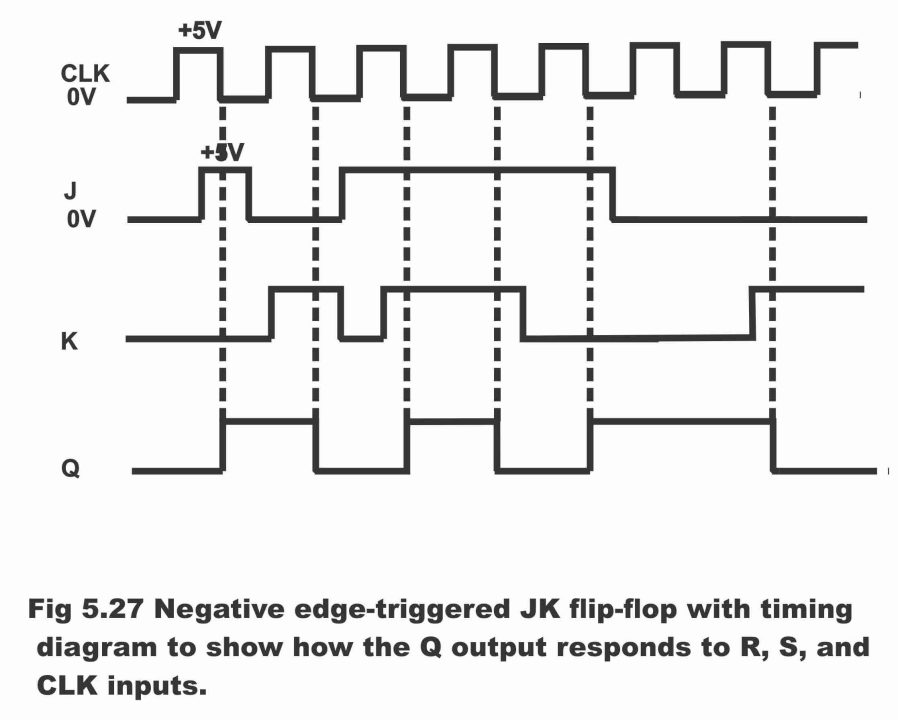

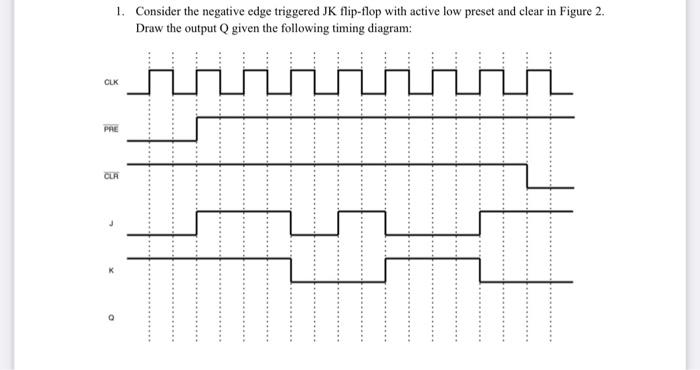

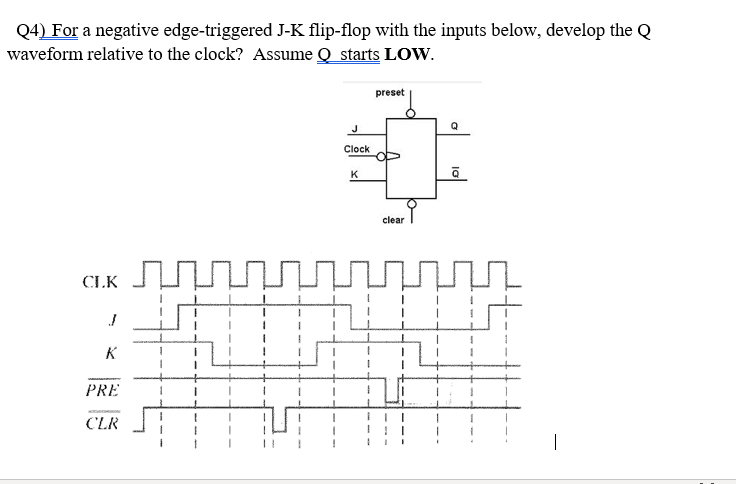

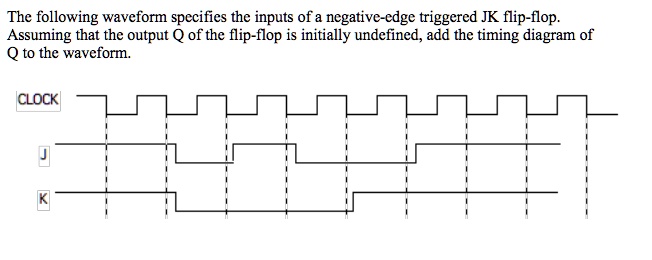

SOLVED: The following waveform specifies the inputs of a negative-edge triggered JK flip-flop. Assuming that the output Q of the flip-flop is initially undefined, add the timing diagram of Q to the

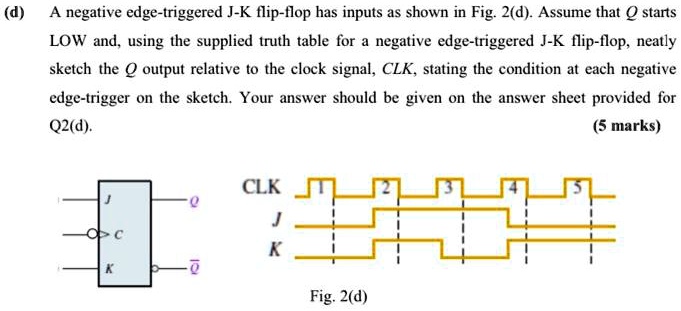

SOLVED: A negative edge-triggered J-K flip-flop has inputs as shown in Fig. 2(d). Assume that Q starts LOW and, using the supplied truth table for a negative edge-triggered J-K flip-flop, neatly sketch

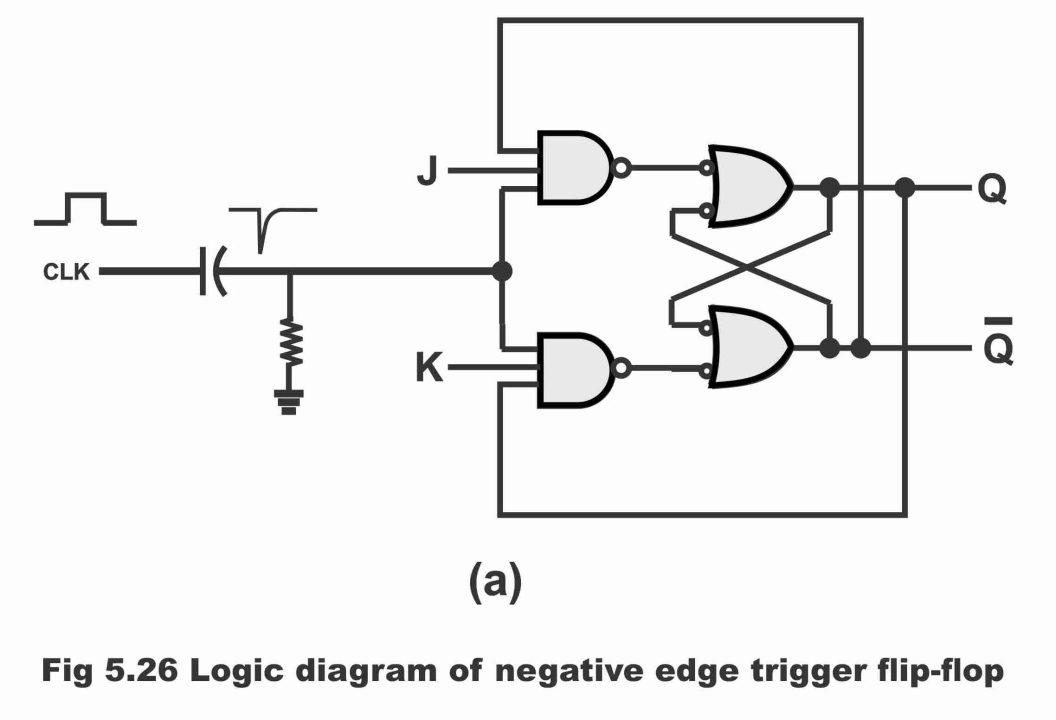

This happens to be a negative edge triggered JK flip flop. I used boolean algebra and found D = E' and E = D'. Given the propagation delay I thought this was

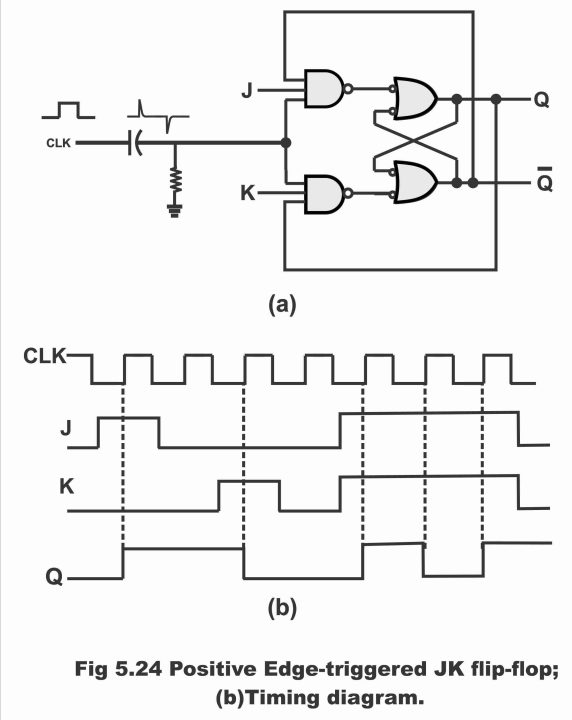

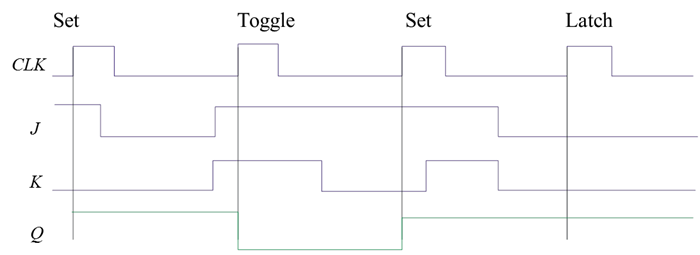

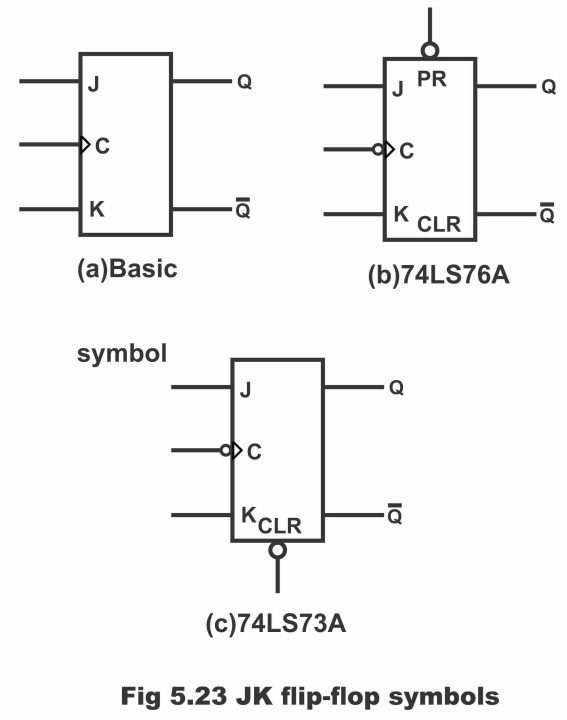

JK Flip-Flop Explained | Race Around Condition in JK Flip-Flop | JK Flip- Flop Truth Table, Excitation table and Timing Diagram - ALL ABOUT ELECTRONICS