microcontroller - Why do we see one, unified memory address space in ARM Cortex-M core based MCUs even though they have Harvard architecture? - Electrical Engineering Stack Exchange

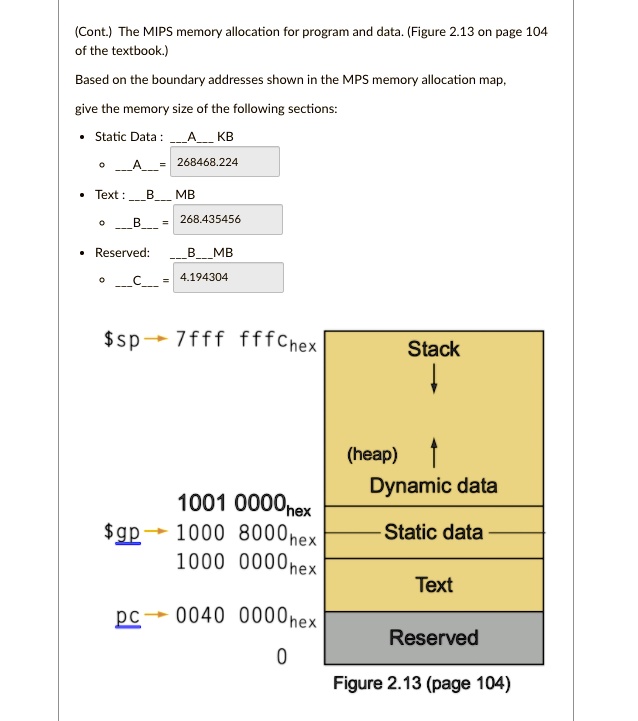

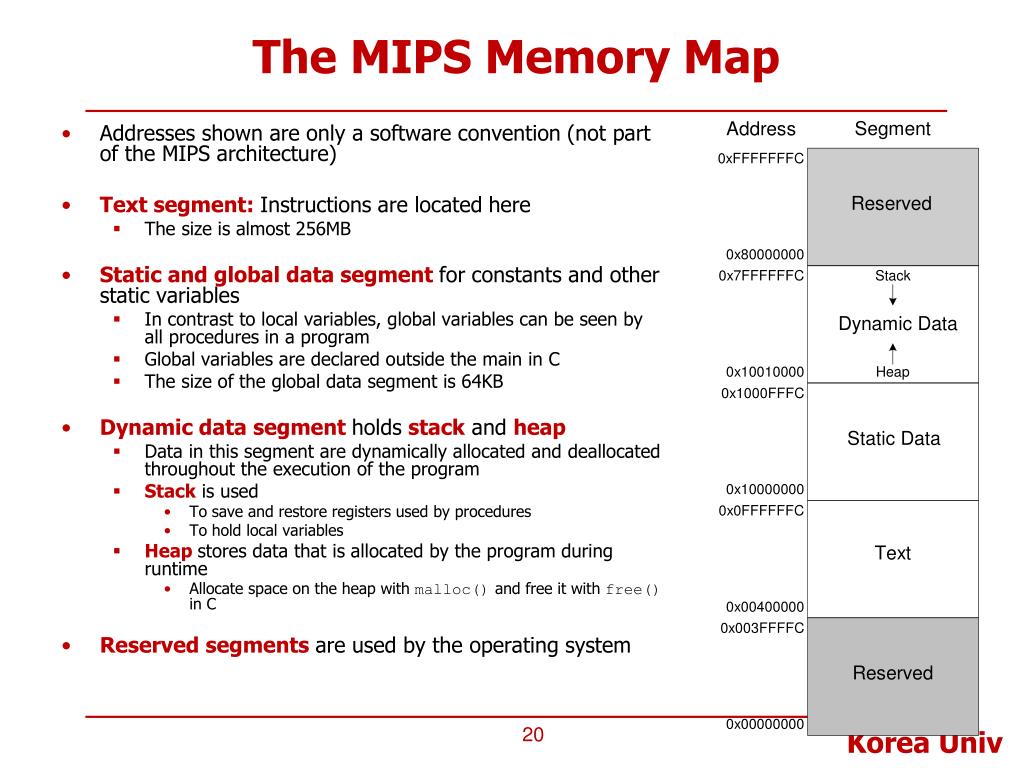

PPT - Lecture 4. Miscellaneous Addressing Mode, Memory Map, Pointer, and ASCII PowerPoint Presentation - ID:3034287

![SOLVED: 5.[10] Show how the following MIPS program would be loaded into memory and executed. # MIPS assembly code Address Segment main: addi sp,sp, -4 Reserved sw ra, 0(sp) addi t0,0, 15 SOLVED: 5.[10] Show how the following MIPS program would be loaded into memory and executed. # MIPS assembly code Address Segment main: addi sp,sp, -4 Reserved sw ra, 0(sp) addi t0,0, 15](https://cdn.numerade.com/ask_images/7659d2f9c991461c81d3a6663a9bba57.jpg)

SOLVED: 5.[10] Show how the following MIPS program would be loaded into memory and executed. # MIPS assembly code Address Segment main: addi sp,sp, -4 Reserved sw ra, 0(sp) addi t0,0, 15