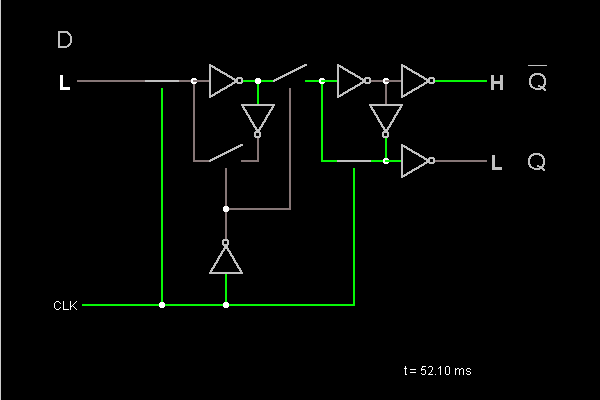

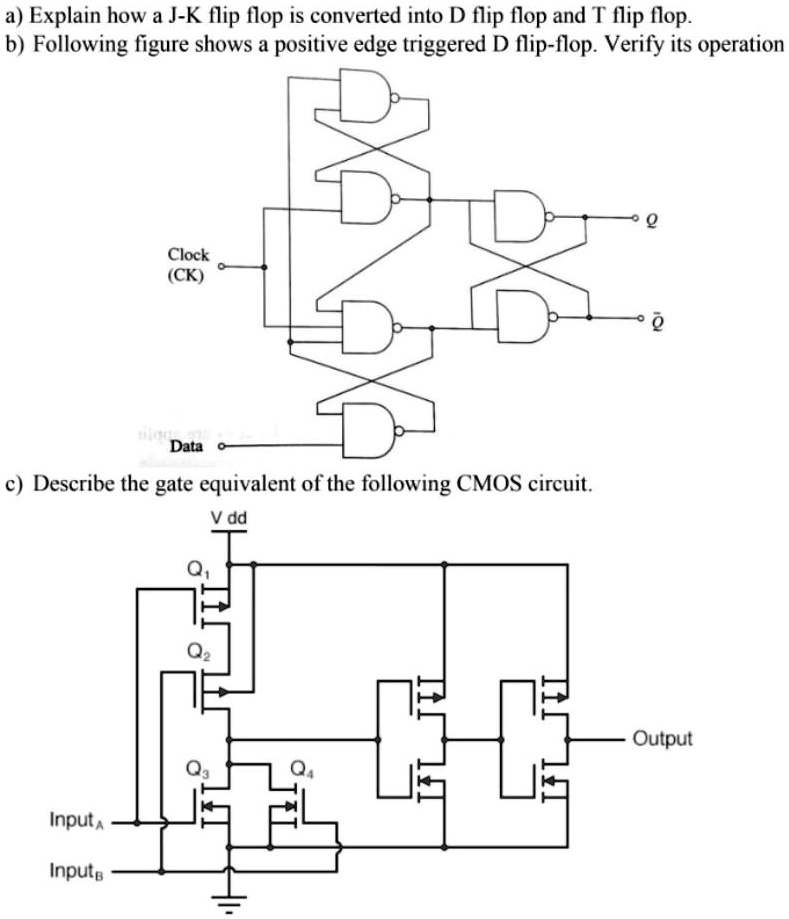

SOLVED: Explain how a J-K flip flop is converted into a D flip flop and T flip flop. Following figure shows a positive edge triggered D flip-flop. Verify its operation. Clock (CK) "

Electronics | Free Full-Text | Design of a Dual Change-Sensing 24T Flip-Flop in 65 nm CMOS Technology for Ultra Low-Power System Chips