Materials | Free Full-Text | Review on Non-Volatile Memory with High-k Dielectrics: Flash for Generation Beyond 32 nm

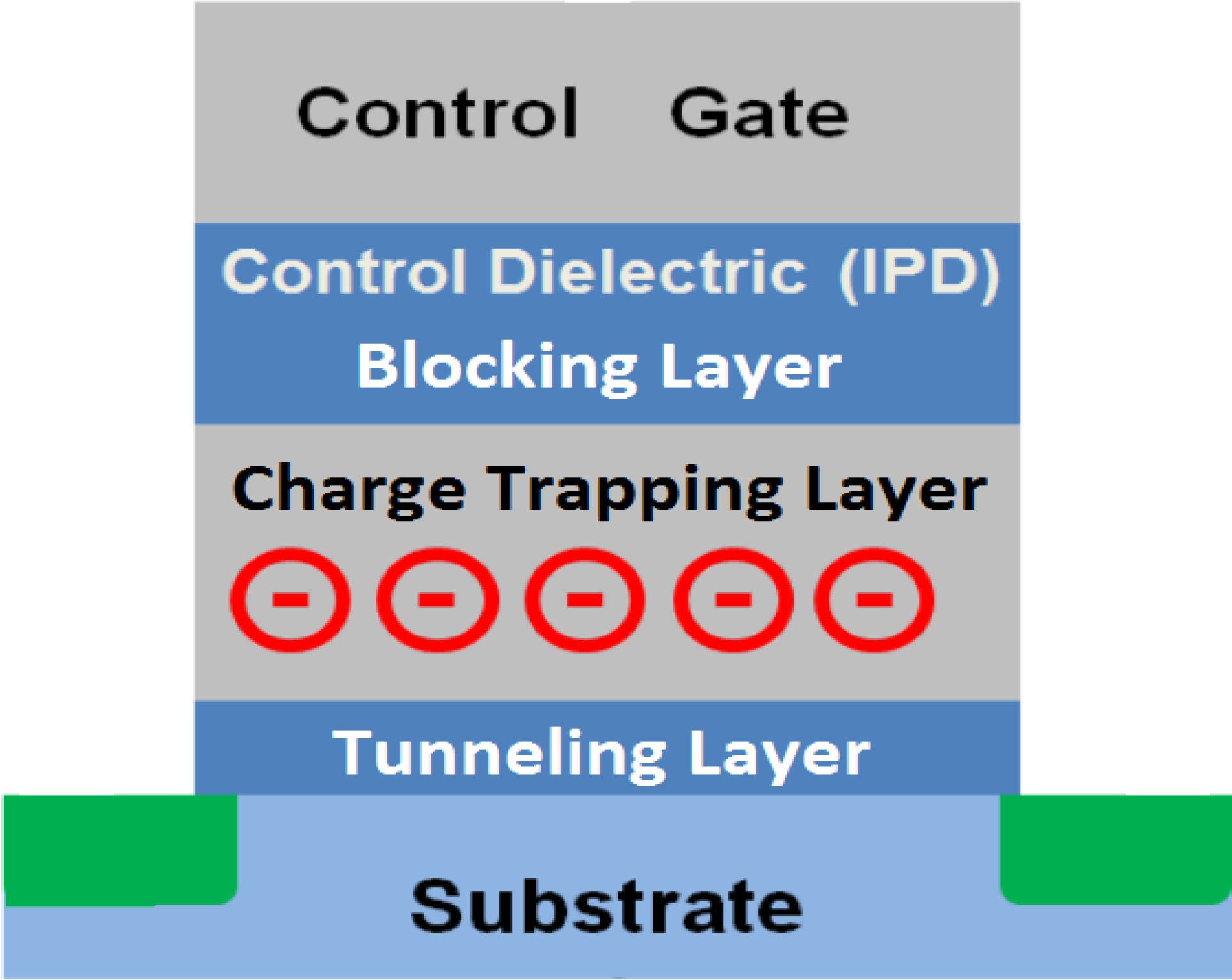

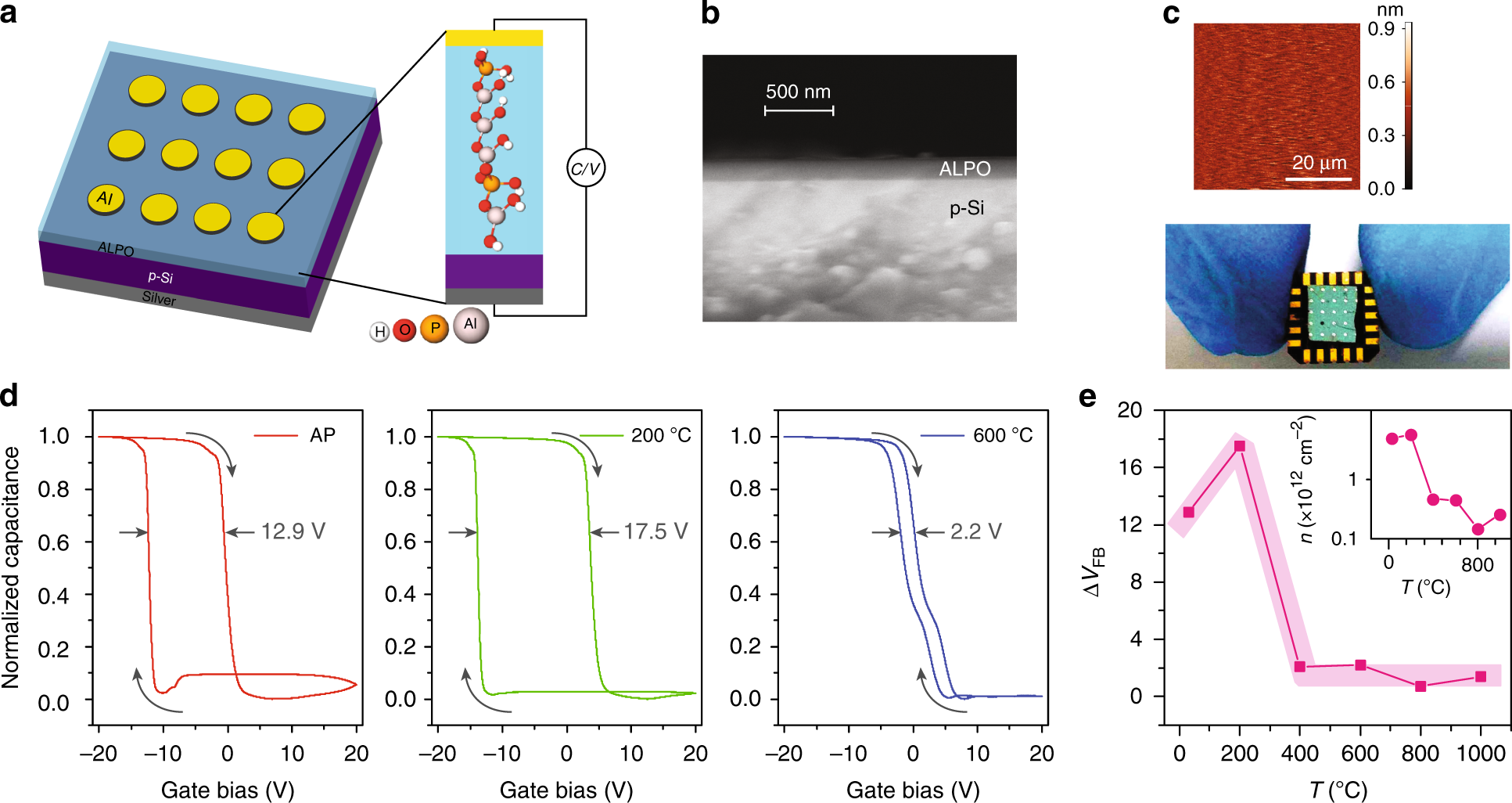

Charge Trapping in Amorphous Dielectrics for Secure Charge Storage | ACS Applied Materials & Interfaces

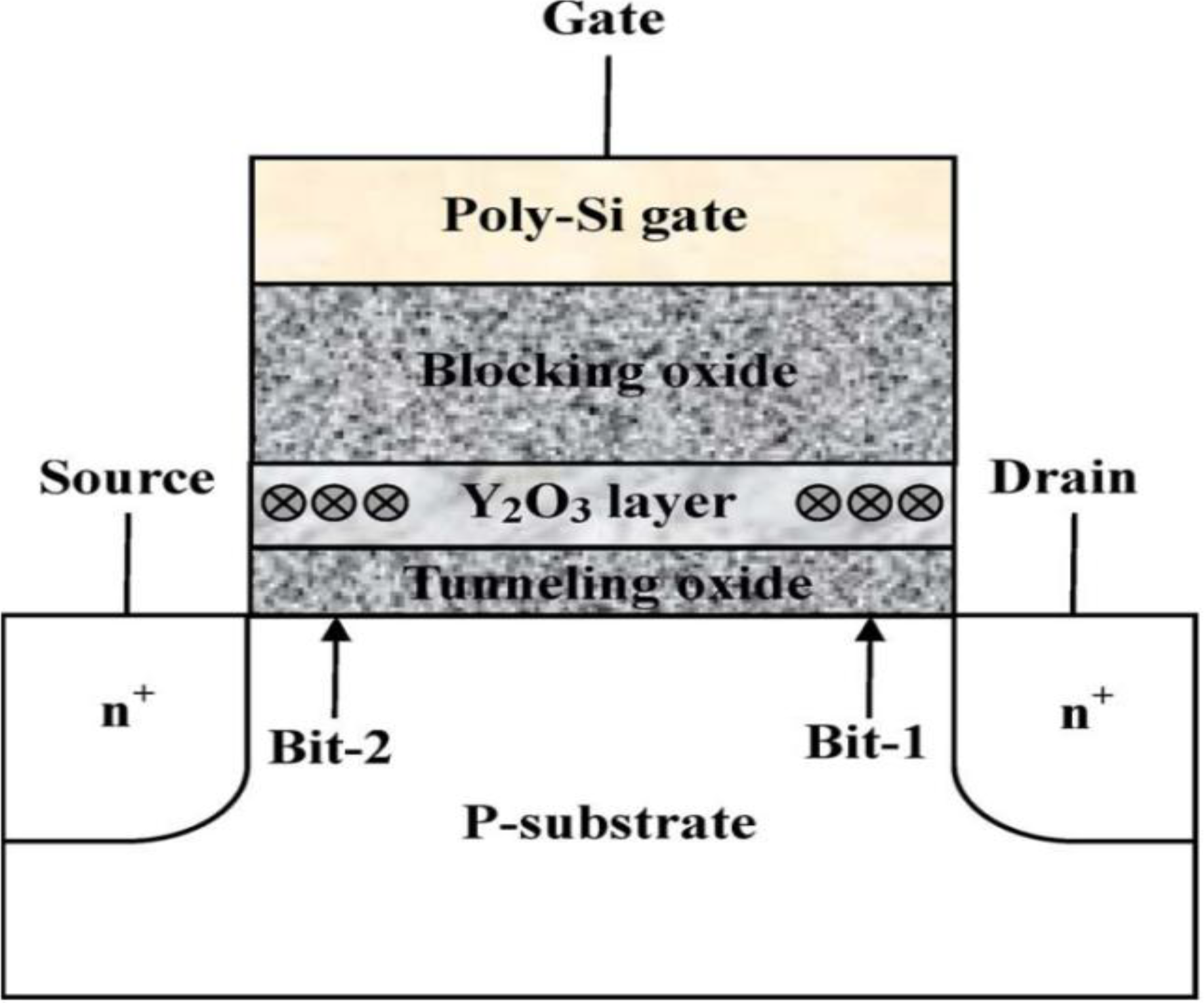

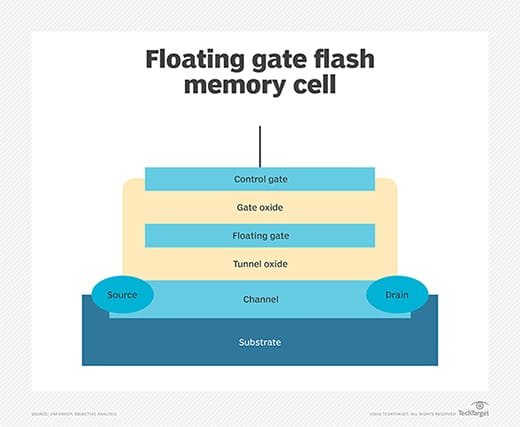

Materials | Free Full-Text | Review on Non-Volatile Memory with High-k Dielectrics: Flash for Generation Beyond 32 nm

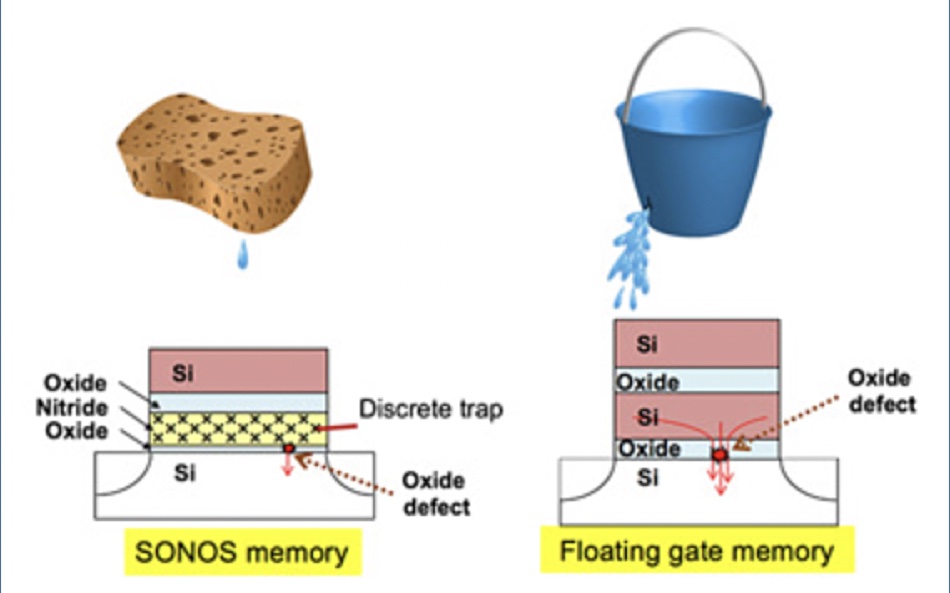

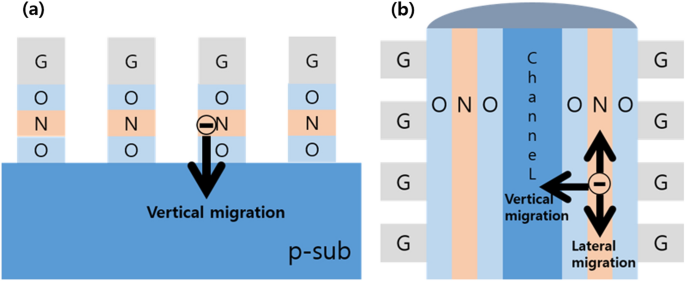

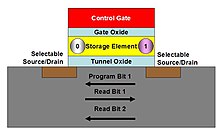

Extraction of Effective Charge Diffusivity in the Charge Trapping Layer of SONOS Flash Memory | SpringerLink

Nanomaterials | Free Full-Text | Optimal Energetic-Trap Distribution of Nano-Scaled Charge Trap Nitride for Wider Vth Window in 3D NAND Flash Using a Machine-Learning Method

Color online) Schematic energy band diagram of fully programed charge... | Download Scientific Diagram

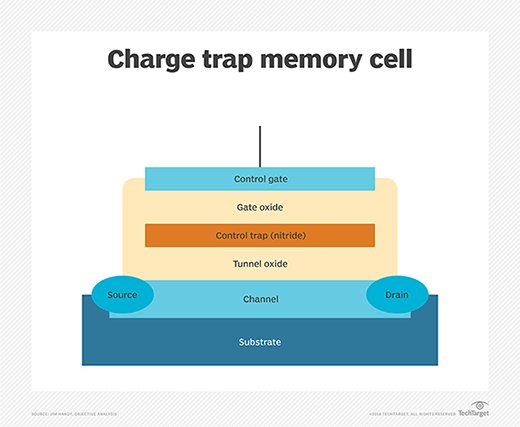

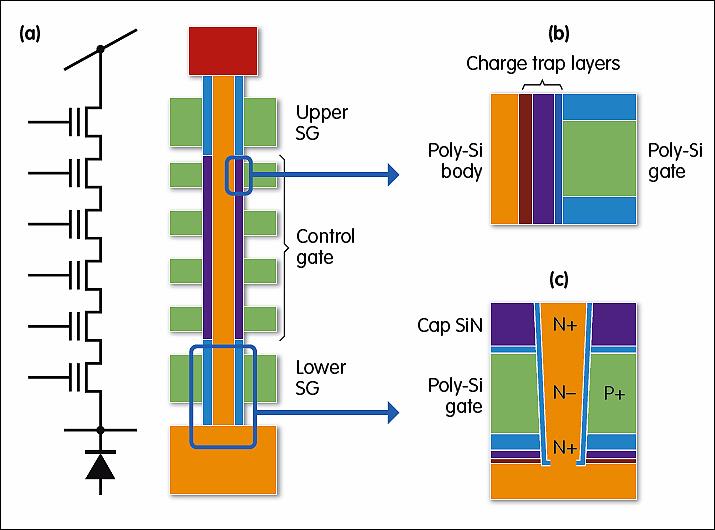

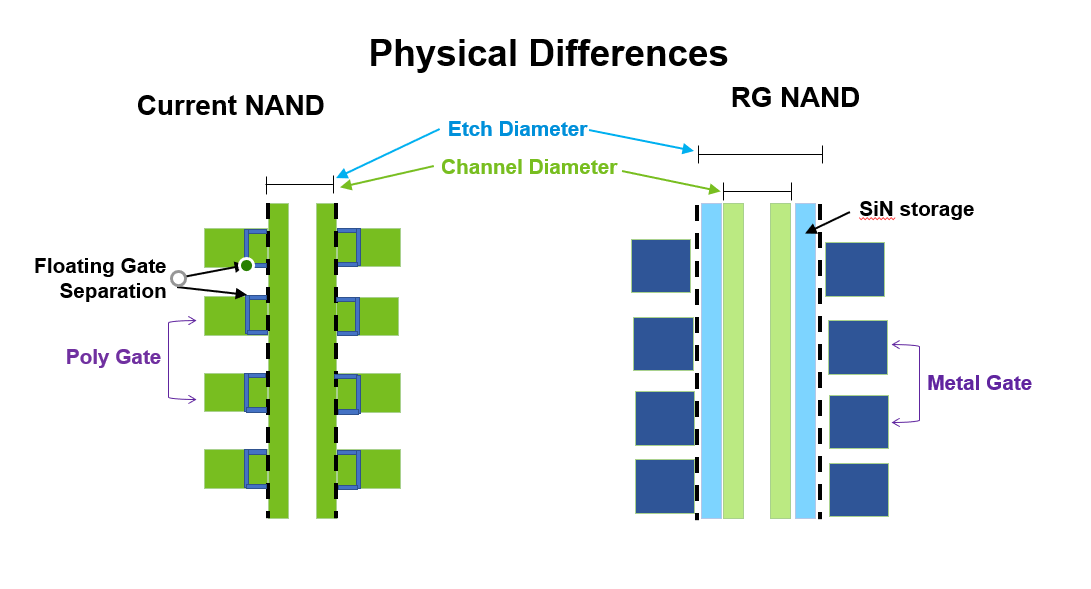

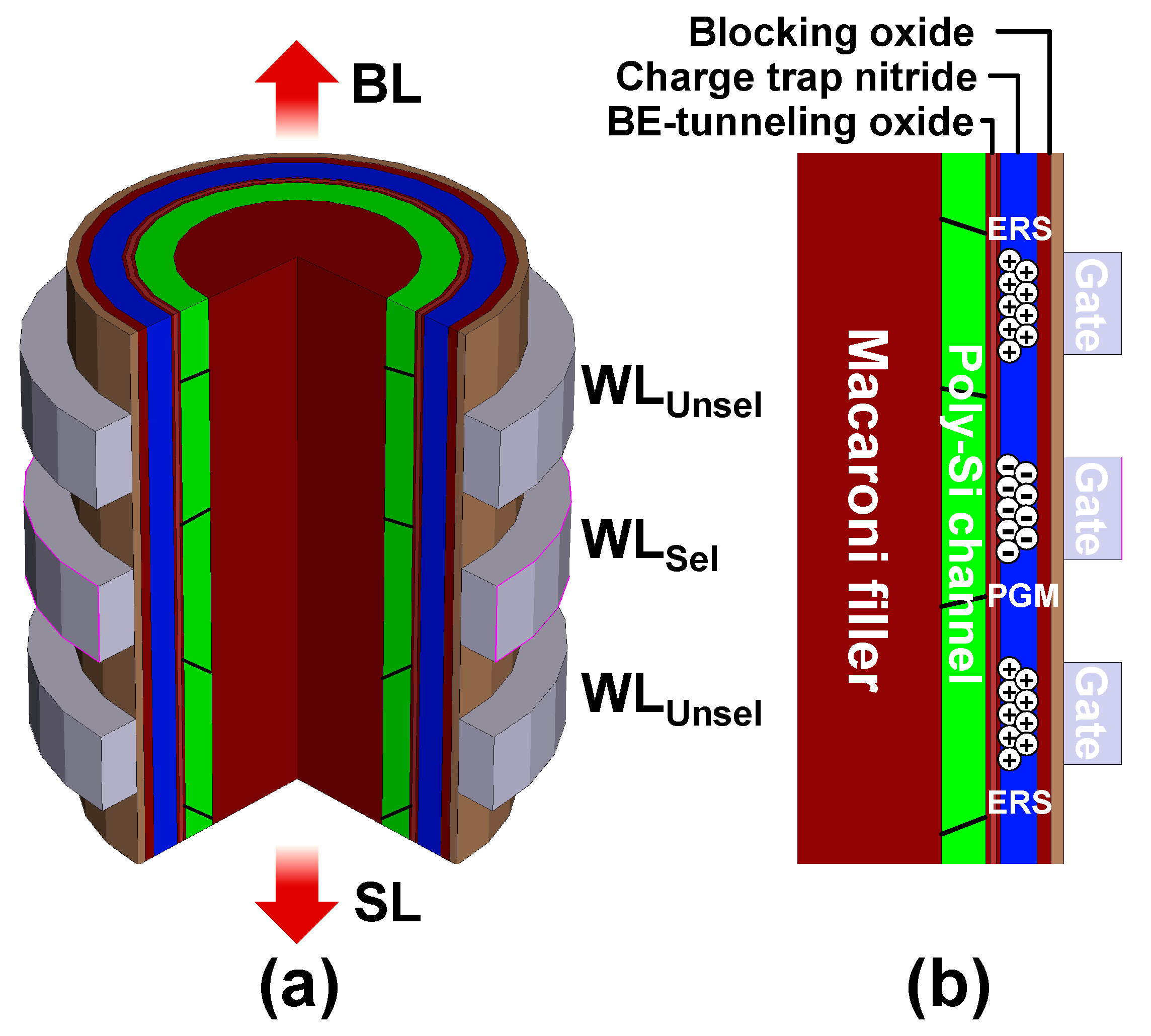

Floating-Gate and Charge-Trap NAND flash cell structure (a), 3D NAND... | Download Scientific Diagram

Low temperature below 200 °C solution processed tunable flash memory device without tunneling and blocking layer | Nature Communications

_en.png)